前置き

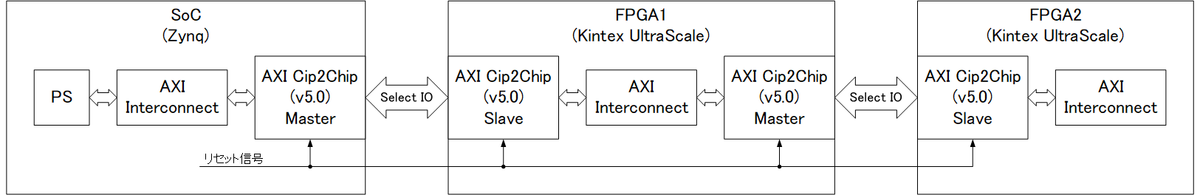

Zynqにぶら下がっている2台のFPGAのレジスタ設定用にAXI Chip2Chip IPを使用しようとしたところ、IPが期待した通りに動かなかったためそのデバッグと対策を行った。

現象

下記系で設計し実機デバッグを行ったところ、SoC-FPGA1間はLinkが立つが、FPGA1-FPGA2間のIPがLinkもErrorも立たない現象が発生した。

IPの外部I/FはSelectIO DDR(Compact 4-1)、AXIバスの接続はAXI Interconnectを使用している。 なお1台のFPGAにAXI Chip2chip IPを2つ置いてインプリを行うとエラーが発生するため、Xilinxのフォーラムなどを参考にIPのMaster/SlaveでIDELAYCTRLとIDELAYE3をグループ分けしている。

調査内容

問題の調査に当たって下記を確認した。

- XilinxのフォーラムやAnswer Recordなどで同様の症状が報告されていないか確認。→なかった。

- 社内実績のあるプロジェクトでFPGAがUltrascaleではなく7シリーズの場合と、Ultrascaleを使用しているが外部I/Fにトランシーバーを使用している場合は同様の問題が発生していなかった。→今回の系特有の問題?

- IP間の信号の接続方法を疑い、シミュレーションをやり直したがそれは問題なかった。→信号の接続の仕方が悪いわけではなさそう。

- FPGA間の信号線が物理的に途切れていることを疑ったが、使用しているIOで別途テスト信号を送受信すると正常にできた。→物理的な信号は問題ない。

- IPの動作モードがCommon/Independentと二つ存在するため、両方試してみたが、どちらでもリンクしなかった。

- IP用のクロックとリセットの仕方の組み合わせをいろいろ変更してみたがどの場合もリンクしなかった。

- IPのバグを疑い、インプリに使用するVivadoのバージョンやAXI Chip2chip IPのバージョンを変更してみたが状況は同じであった。

- IDELAYCTRLとIDELAYE3をグループ分けしないとインプリが通らない事やSoC-FPGA1間はリンクしていることから、1つのFPGAにIPが1つなら問題ないのかと考え、試しにSoC-FPGA1間のIPを削除してみたらFPGA1-FPGA2間のIPがリンクした→IPが複数あることが原因?

- IPからはクロックとデータが入出力されるが、クロックは問題なく出ている。ただしIP起動時のリンク用のデータ出力が途中で止まってしまっている。→IP内部の起動シーケンスがおかしくなっていそう。

フォーラムなどを見ると「FPGAが7シリーズで外部I/FがSelectIO」か「FPGAがUltrascaleで外部I/Fがトランシーバー」のケースしか見かけられなかったため、「FPGAがUltrascaleで外部I/FがSelectIO」という組み合わせで発生するバグか、もしくはその組み合わせの際に特別に何か設定する必要があるかのどちらかが原因と思われるが、情報が少なくまたIP内部のシーケンスの問題の場合は対処の方法がないためこれ以上のデバッグは断念した。

行った対応

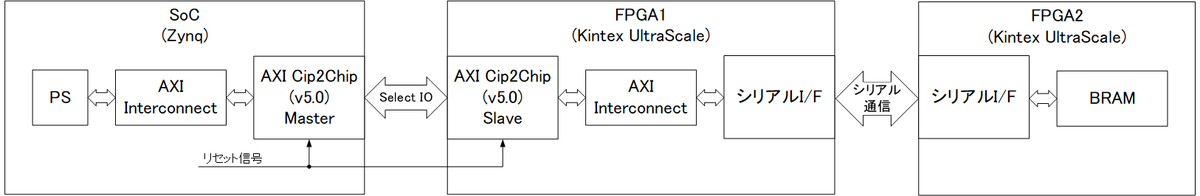

SoC-FPGA1間の動作は問題なかったことと、FPGA1-FPGA2間の接続はレジスタの設定/読み出しのみで遅延をあまり考える必要がなく複雑な処理も必要なかったため、FPGA1-FPGA2間のみ外部I/Fを自作のシリアル通信I/Fに変更して対処した。

今回の系では外部I/FにSelectIOを使用していたが、トランシーバーを使用した方がFPGA間の信号の接続本数が少なくて済みいろいろと考える必要が少ないため、今後同じ問題に当たる可能性は低いかもしれないが参考のため記録に残しておく。